자동차 비전용 SoC 개발동향

페이지 정보

글 : 채영석(webmaster@global-autonews.com)|

|

승인 2014-11-06 03:26:02 |

본문

1. 서론

구글의 무인 자율주행 자동차는 비디오 카메라, 레이더/레이저 등의 다양한 센서들을 이용하여 도로와 장 애물을 인식하여 80만 km를 사고 없이 안전하게 주행하였다 �. 구글은 이를 바탕으로 100대의 무인자동차 프로토타입을 추가 개발, 운용하여 2017년 자율주행 자동차의 상용화를 계획하고 있다. 뿐만아니라 벤츠, 아우디, 도요타, 닛산, 현대-기아 등 국내외 완성차 업체 또한 2020년을 기점으로 자율주행 자동차의 출시 계획을 발표한 바 있다.

글 / 민경원 (전자부품연구원)

출처 / 오토저널 8월호

구글이 개발한 자율주행 자동차의 가격은 대략 15만 달러(한화 1억 6천만 원)로 그 중에서 도로 상황과 장 애물을 검지하는 핵심 센서인 3D 스캔 라이다 및 레이더 센서 기반 시스템이 약 7만 달러(한화 7.7천만 원) 를 차지하고 있어 본격적인 상용화를 위해서는 상당한 노력이 요구될 것으로 보인다.

이에 따라 완성차 업체는 다양한 도로상황 및 장애물 인식을 효과적으로 수행 가능한 카메라를 핵심 센서 로 이용하여 컴퓨터비젼 신호처리를 수행함으로써 ADAS(Advanced Driver Assistant System) 뿐 아니라 무인 주행 자동차를 구현하기 위한 연구를 진행하고 있다.

카메라 센서를 이용하는 컴퓨터비전 신호처리 기술은 레이다 또는 레이저를 이용하는 다른 기술들보다 가격이 싸고 다양한 기능을 동시 구현 할 수 있다는 장점이 있다. 카메라 센서에서 수집한 정보는 영상 처리 및 분석을 통해 차량 또는 보행자의 유/무 여부와 거리 측정, 신호등 및 교통 표지판 인식, 차선 인식, 차선 변경 여부 판단, 사각지대 감지, 자동 주차 등에 사용할 수 있다. 그러나 카메라를 통해 입력된 2D 기반의 영 상을 분석하여 신호처리를 수행해야 하므로 고성능의 2차원 컴퓨터 비전 신호처리 기능을 요구한다.

컴퓨터 비전 기술은 영상처리 분야에서 오랫동안 연구되어 왔다. 기존의 컴퓨터 비전 기술은 주로 컴퓨터 를 기반으로 한 시스템 상에서 구현 되었으나 최근 들어 지능형 자동차, 지능형 로봇과 같이 임베디드 시스 템 형태로 개별 장치에 탑재되는 임베디드 비전 시스템(Embedded Vision System)이 급격히 확대되고 있 다. 기존의 컴퓨터 대비 소형, 저전력 구현이 요구되는 임베디드 시스템은 상대적으로 낮은 연산 성능의 프 로세서가 탑재 가능하므로 많은 개발자들은 범용 마이크로프로세서를 이용하는 대신 낮은 수준의 일부 산술 적 연산을 빠른 속도로 처리 가능한 DSP를 이용하여 임베디드 솔루션을 개발해 왔다.

그러나 급격한 임베디드 시스템용 프로세서의 성능 향상에도 불구하고, 프로세서 기반의 솔루션은 2차원 적인 컴퓨터 비전의 연산 처리 요구량을 충족시키는데 한계를 노출하고 있다. 이에 따라 최근 상용화되고 있 는 차량용 임베디드 비젼 시스템에는 임베디드 프로세서와 전용의 논리회로 기반 가속 하드웨어 로직을 하 나의 칩에 구현하는 SoC(System on a Chip)가 개발되어 탑재되고 있다.

2. 자동차 비전용 SoC 개발 현황

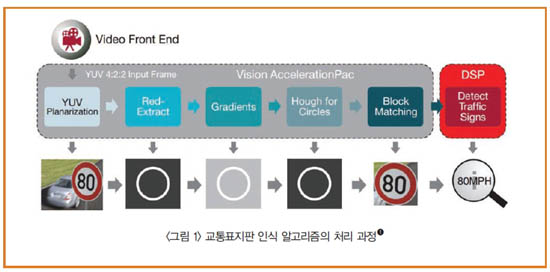

그림 1은 속도제한 표지판을 인식하는 비전 알고리즘을 구현하는 일반적인 방법을 나타낸 것이다. 먼저 카메라 센서에서 입력된 영상은 ISP(Image Signal Processor)에서 카메라에 의한 영상 왜곡 보정과 입력 영상에 대한 전처리 과정을 거쳐 영상 버퍼에 저장한다. 버퍼에 저장된 2차원 영상에서 교통 표지판을 나타 내는 붉은 색과 아닌 영역을 구분한다. 그리고 원을 찾기 위한 기울기값(Gradient)추출과정과 허프(Hough) 변환 과정을 거쳐 영상 중에서 표지판이 있는 영역인 ROI(Region of Interest)를 찾는다. 이 ROI에 대해 저 장된 표지판 이미지와 템플리트(Template)매칭 연산을 수행하여 도출된 정합도에 따라 최종적으로 교통 표 지판의 정보를 판별한다.

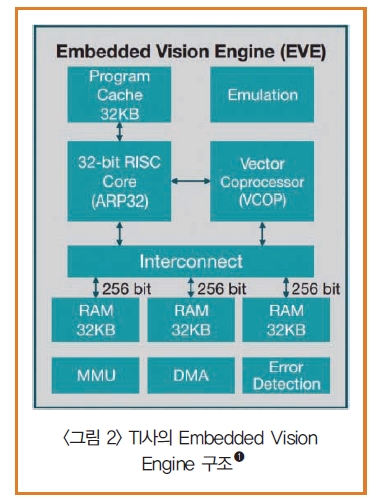

EVE는 그림 2와 같이 275Mhz로 구동되는 RISC 코어 와 550MHz로 동작하는 SIMD 기반의 벡터 프로세서인 VCOP(Vector COProcessor)를 내장하여 2차원 기반 영상 데이터를 처리한다.

이와 유사하게 NVIDIA는 ARM 쿼드 코어와 192개 GPU 코어를 내장하여 신호등 인식, 사각지대탐지, 차선이탈경보, 운전자상태 모니터링, 주차보조 등의 어플리케이션을 구현 가능한 GPGPU(General- Purpose computing on Graphics Processing Units)인 Tegra SoC를 출시하였다.

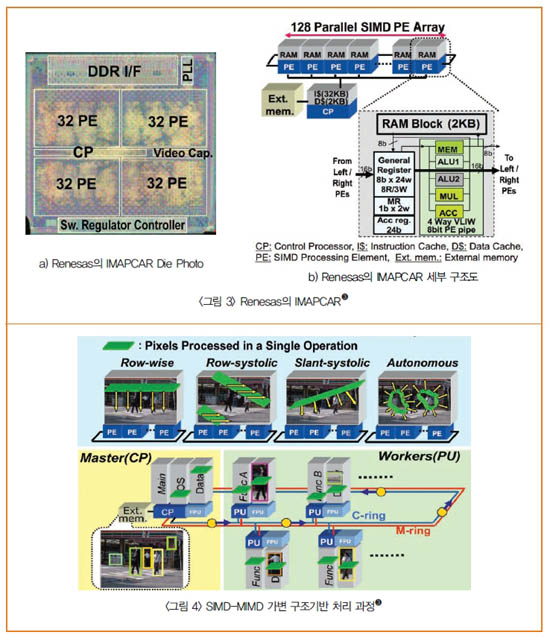

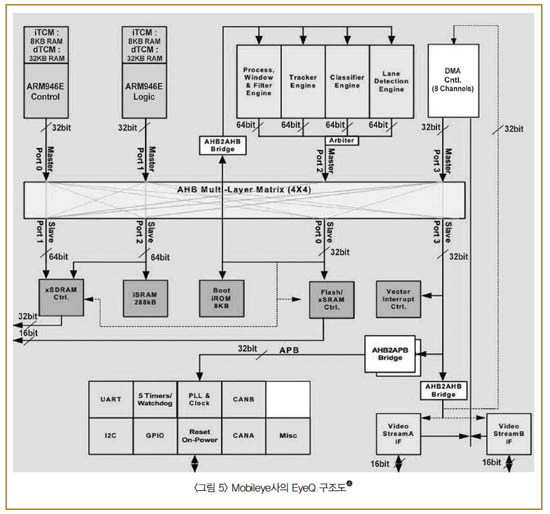

Mobileye는 EyeQ SoC 시리즈를 개발하여 차선 검출, 차량 검출 및 거리 인식 및 교통 신호 인식 등의 기 능을 제공하는 영상기반 ADAS용 SoC를 공급하고 있다. Mobileye의 EyeQ는 그림 5와 같이 Filter, Tracker, Classifier, Lane Detection 기능을 갖는 4개의 영상처리전용 엔진인 VCEs(Vision Computing Engines)와 시스템 제어 및 응용 프로그램 수행을 위한 32비트 듀얼 ARM RISC 프로세서를 탑재하고 있 다. EyeQ는 영상기반 ADAS에 특화전 전용 엔진을 통해 FCW(Forward Collision Warning), 차선, 표지판 인식 등의 어플리케이션을 동시에 고속 처리 가능하도록 설계되었다.

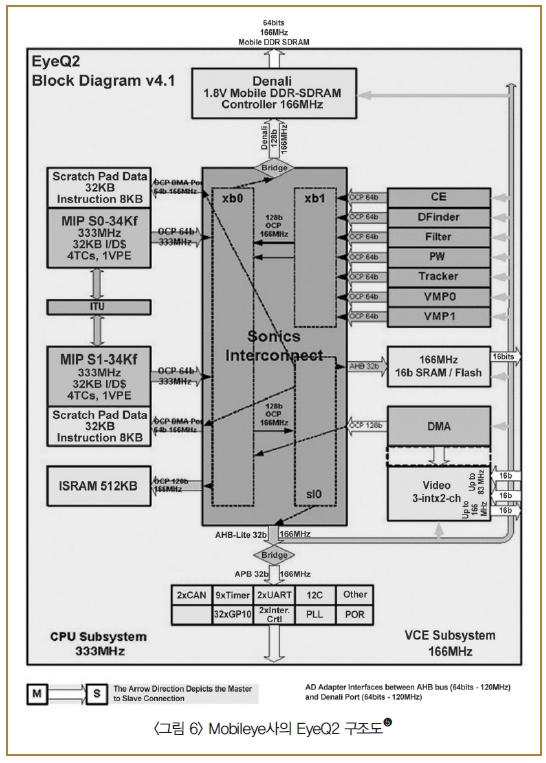

EyeQ의 후속 제품인 EyeQ2는 <그림 6>과 같이 두 개의 MIPS34K RISC 코어 프로세서를 탑재하고 있으 며, 영상인식 처리 속도 향상을 위해 Classifier, Tracker, Disparity Detecter, Filter 연산기로 구성된 전 용 가속기 엔진인 Vision Computing Engine과 SIMD 기반의 세 개의 VMP (Vector Microcode Machine)을 사용하여 영상기반 ADAS를 위한 알고리즘을 보다 프로그래머블하게 구현할 수 있도록 설계되었다.

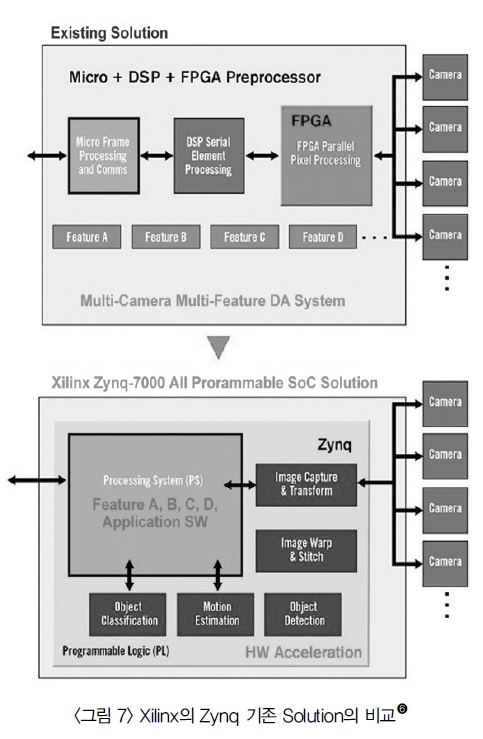

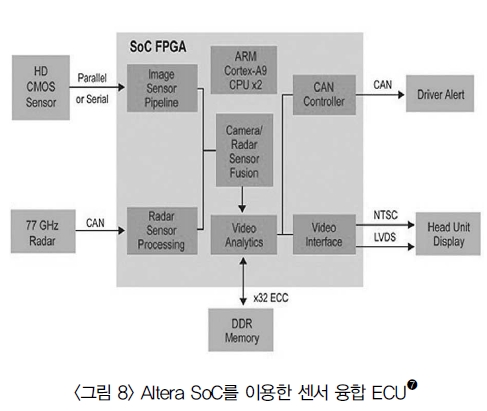

FPGA는 전통적으로 병렬처리를 위한 논 리회로를 어플리케이션에 따라 프로그래머 블하게 탑재하기 위한 용도로 사용되어 왔 으나, 최근에 발표된 FPGA는 프로그래밍 로직 뿐 아니라 모바일 시장에서 동작 및 성 능이 검증된 ARM사의 Cortex A9 프로세 서를 FPGA 내에 탑재하여 하드웨어와 소프 트웨어를 동시에 구현할 수 있고, 소프트웨 어를 600MHz 이상의 클럭으로 동작시키는 프로그래머블 SoC의 형태로 진화하고 있다. Xilinx는 ARM의 Cortex A9 프로세서 2 개와 대용량 데이터를 병렬 처리할 수 있는 프로그래머블 로직을 동시에 탑재하고 외부 에 DRAM, 버스와 I2C, SPI, UART 등의 주변 장치를 연결할 수 있는 Zynq SoC를 개발하였는데, 이 솔루션은 <그림 7>과 같이 마이크로프로세서, DSP, FPGA를 하나의 칩에 통합함으로 시스템 성능을 향상시키고 전력소모와 시스템 설계 비용을 감소시킬 수 있는 장점이 있다.

어플리케이션에 맞는 전용 엔진을 개발하여야 하므로 상대적으 로 개발기간 길어지고 응용분야가 제한된다는 단점이 있다.

3. 결론

EURO-NCAP과 같은 차량안전, 교통사고 예방을 위한 규 제강화에 따라 안전성과 편의성을 요구하는 지능형 자동차 시 장은 점차 확대되고 있으며 이에따라 다양한 ADAS응용 시스 템을 낮은 가격으로 동시 처리 가능한 영상기반 ADAS시스템 에 대한 요구도 급격히 증가하고 있다. 자동차 비전용 SoC는 이와 같은 시장의 요구에 부응하여 임베디드 컴퓨터 비젼을 구 현하는 핵심 요소로 낮은 개발 비용과 높은 처리 성능을 제공 가능하므로 향후 다양한 형태의 제품과 솔루션들이 출시될 것 으로 예상된다.

구글의 무인 자율주행 자동차는 비디오 카메라, 레이더/레이저 등의 다양한 센서들을 이용하여 도로와 장 애물을 인식하여 80만 km를 사고 없이 안전하게 주행하였다 �. 구글은 이를 바탕으로 100대의 무인자동차 프로토타입을 추가 개발, 운용하여 2017년 자율주행 자동차의 상용화를 계획하고 있다. 뿐만아니라 벤츠, 아우디, 도요타, 닛산, 현대-기아 등 국내외 완성차 업체 또한 2020년을 기점으로 자율주행 자동차의 출시 계획을 발표한 바 있다.

글 / 민경원 (전자부품연구원)

출처 / 오토저널 8월호

구글이 개발한 자율주행 자동차의 가격은 대략 15만 달러(한화 1억 6천만 원)로 그 중에서 도로 상황과 장 애물을 검지하는 핵심 센서인 3D 스캔 라이다 및 레이더 센서 기반 시스템이 약 7만 달러(한화 7.7천만 원) 를 차지하고 있어 본격적인 상용화를 위해서는 상당한 노력이 요구될 것으로 보인다.

이에 따라 완성차 업체는 다양한 도로상황 및 장애물 인식을 효과적으로 수행 가능한 카메라를 핵심 센서 로 이용하여 컴퓨터비젼 신호처리를 수행함으로써 ADAS(Advanced Driver Assistant System) 뿐 아니라 무인 주행 자동차를 구현하기 위한 연구를 진행하고 있다.

카메라 센서를 이용하는 컴퓨터비전 신호처리 기술은 레이다 또는 레이저를 이용하는 다른 기술들보다 가격이 싸고 다양한 기능을 동시 구현 할 수 있다는 장점이 있다. 카메라 센서에서 수집한 정보는 영상 처리 및 분석을 통해 차량 또는 보행자의 유/무 여부와 거리 측정, 신호등 및 교통 표지판 인식, 차선 인식, 차선 변경 여부 판단, 사각지대 감지, 자동 주차 등에 사용할 수 있다. 그러나 카메라를 통해 입력된 2D 기반의 영 상을 분석하여 신호처리를 수행해야 하므로 고성능의 2차원 컴퓨터 비전 신호처리 기능을 요구한다.

컴퓨터 비전 기술은 영상처리 분야에서 오랫동안 연구되어 왔다. 기존의 컴퓨터 비전 기술은 주로 컴퓨터 를 기반으로 한 시스템 상에서 구현 되었으나 최근 들어 지능형 자동차, 지능형 로봇과 같이 임베디드 시스 템 형태로 개별 장치에 탑재되는 임베디드 비전 시스템(Embedded Vision System)이 급격히 확대되고 있 다. 기존의 컴퓨터 대비 소형, 저전력 구현이 요구되는 임베디드 시스템은 상대적으로 낮은 연산 성능의 프 로세서가 탑재 가능하므로 많은 개발자들은 범용 마이크로프로세서를 이용하는 대신 낮은 수준의 일부 산술 적 연산을 빠른 속도로 처리 가능한 DSP를 이용하여 임베디드 솔루션을 개발해 왔다.

그러나 급격한 임베디드 시스템용 프로세서의 성능 향상에도 불구하고, 프로세서 기반의 솔루션은 2차원 적인 컴퓨터 비전의 연산 처리 요구량을 충족시키는데 한계를 노출하고 있다. 이에 따라 최근 상용화되고 있 는 차량용 임베디드 비젼 시스템에는 임베디드 프로세서와 전용의 논리회로 기반 가속 하드웨어 로직을 하 나의 칩에 구현하는 SoC(System on a Chip)가 개발되어 탑재되고 있다.

2. 자동차 비전용 SoC 개발 현황

그림 1은 속도제한 표지판을 인식하는 비전 알고리즘을 구현하는 일반적인 방법을 나타낸 것이다. 먼저 카메라 센서에서 입력된 영상은 ISP(Image Signal Processor)에서 카메라에 의한 영상 왜곡 보정과 입력 영상에 대한 전처리 과정을 거쳐 영상 버퍼에 저장한다. 버퍼에 저장된 2차원 영상에서 교통 표지판을 나타 내는 붉은 색과 아닌 영역을 구분한다. 그리고 원을 찾기 위한 기울기값(Gradient)추출과정과 허프(Hough) 변환 과정을 거쳐 영상 중에서 표지판이 있는 영역인 ROI(Region of Interest)를 찾는다. 이 ROI에 대해 저 장된 표지판 이미지와 템플리트(Template)매칭 연산을 수행하여 도출된 정합도에 따라 최종적으로 교통 표 지판의 정보를 판별한다.

EVE는 그림 2와 같이 275Mhz로 구동되는 RISC 코어 와 550MHz로 동작하는 SIMD 기반의 벡터 프로세서인 VCOP(Vector COProcessor)를 내장하여 2차원 기반 영상 데이터를 처리한다.

이와 유사하게 NVIDIA는 ARM 쿼드 코어와 192개 GPU 코어를 내장하여 신호등 인식, 사각지대탐지, 차선이탈경보, 운전자상태 모니터링, 주차보조 등의 어플리케이션을 구현 가능한 GPGPU(General- Purpose computing on Graphics Processing Units)인 Tegra SoC를 출시하였다.

Mobileye는 EyeQ SoC 시리즈를 개발하여 차선 검출, 차량 검출 및 거리 인식 및 교통 신호 인식 등의 기 능을 제공하는 영상기반 ADAS용 SoC를 공급하고 있다. Mobileye의 EyeQ는 그림 5와 같이 Filter, Tracker, Classifier, Lane Detection 기능을 갖는 4개의 영상처리전용 엔진인 VCEs(Vision Computing Engines)와 시스템 제어 및 응용 프로그램 수행을 위한 32비트 듀얼 ARM RISC 프로세서를 탑재하고 있 다. EyeQ는 영상기반 ADAS에 특화전 전용 엔진을 통해 FCW(Forward Collision Warning), 차선, 표지판 인식 등의 어플리케이션을 동시에 고속 처리 가능하도록 설계되었다.

EyeQ의 후속 제품인 EyeQ2는 <그림 6>과 같이 두 개의 MIPS34K RISC 코어 프로세서를 탑재하고 있으 며, 영상인식 처리 속도 향상을 위해 Classifier, Tracker, Disparity Detecter, Filter 연산기로 구성된 전 용 가속기 엔진인 Vision Computing Engine과 SIMD 기반의 세 개의 VMP (Vector Microcode Machine)을 사용하여 영상기반 ADAS를 위한 알고리즘을 보다 프로그래머블하게 구현할 수 있도록 설계되었다.

FPGA는 전통적으로 병렬처리를 위한 논 리회로를 어플리케이션에 따라 프로그래머 블하게 탑재하기 위한 용도로 사용되어 왔 으나, 최근에 발표된 FPGA는 프로그래밍 로직 뿐 아니라 모바일 시장에서 동작 및 성 능이 검증된 ARM사의 Cortex A9 프로세 서를 FPGA 내에 탑재하여 하드웨어와 소프 트웨어를 동시에 구현할 수 있고, 소프트웨 어를 600MHz 이상의 클럭으로 동작시키는 프로그래머블 SoC의 형태로 진화하고 있다. Xilinx는 ARM의 Cortex A9 프로세서 2 개와 대용량 데이터를 병렬 처리할 수 있는 프로그래머블 로직을 동시에 탑재하고 외부 에 DRAM, 버스와 I2C, SPI, UART 등의 주변 장치를 연결할 수 있는 Zynq SoC를 개발하였는데, 이 솔루션은 <그림 7>과 같이 마이크로프로세서, DSP, FPGA를 하나의 칩에 통합함으로 시스템 성능을 향상시키고 전력소모와 시스템 설계 비용을 감소시킬 수 있는 장점이 있다.

어플리케이션에 맞는 전용 엔진을 개발하여야 하므로 상대적으 로 개발기간 길어지고 응용분야가 제한된다는 단점이 있다.

3. 결론

EURO-NCAP과 같은 차량안전, 교통사고 예방을 위한 규 제강화에 따라 안전성과 편의성을 요구하는 지능형 자동차 시 장은 점차 확대되고 있으며 이에따라 다양한 ADAS응용 시스 템을 낮은 가격으로 동시 처리 가능한 영상기반 ADAS시스템 에 대한 요구도 급격히 증가하고 있다. 자동차 비전용 SoC는 이와 같은 시장의 요구에 부응하여 임베디드 컴퓨터 비젼을 구 현하는 핵심 요소로 낮은 개발 비용과 높은 처리 성능을 제공 가능하므로 향후 다양한 형태의 제품과 솔루션들이 출시될 것 으로 예상된다.